# CARACTERIZACIÓN DE TRANSISTORES HEMT EN BANDA Q

MEMORIA PARA OPTAR AL TÍTULO DE INGENIERO CIVIL ELÉCTRICO

## FRANCISCO JOSÉ NAVARRETE MORENO

PROFESOR GUÍA: SR. PATRICIO MENA MENA

MIEMBROS DE LA COMISIÓN: SR. NICOLÁS REYES GUZMÁN SR. LEONARDO BRONFMAN AGUILO

> SANTIAGO DE CHILE JULIO 2011

RESUMEN DE LA MEMORIA PARA OPTAR AL TÍTULO DE INGENIERO CIVIL ELECTRICISTA POR: FRANCISCO NAVARRETE

FECHA: 18 DE JULIO DE 2011

PROF. GUÍA: SR. PATRICIO MENA MENA

# "DISEÑO Y CONSTRUCCIÓN DE UN AMPLICADOR DE BAJO RUIDO BASADO EN TRANSISTORES DISCRETOS"

Este trabajo de título tiene como objetivo diseñar y construir un sistema de caracterización de transistores HEMT. Este sistema tiene como fin determinar el comportamiento de transistores candidatos a ser utilizados en el diseño de amplificadores de bajo ruido para receptores de antenas radioastronomicas que operen en Banda 1 del proyecto ALMA.

Como parte de este sistema se diseñaron y construyeron dos módulos, un módulo Bias Tee y un sistema de calibración TRL. El módulo Bias Tee permite mezclar, por un mismo canal, la señal proveniente del VNA y la polarización para entregarselas al transistor. El módulo de calibración TRL permite descontar de la medición de parámetros S del transistor, el efecto del resto de los elementos que forman el sistema de caracterización. Además, se desarrolló un software que a partir de los datos obtenidos del transistor calcula sus parámetros S.

Al realizar las mediciones del módulo Bias Tee y del sistema de calibración, estas diferían del comportamiento que mostraban las simulaciones. En el caso del Bias Tee se encontró que la mayor parte de la señal incidente en el módulo se refleja. En el caso del sistema de calibración, se genera una calibración exitosa pero altamente sensible a las modificaciones en el montaje, lo que no permite obtener una calibración estable para medir el transistor.

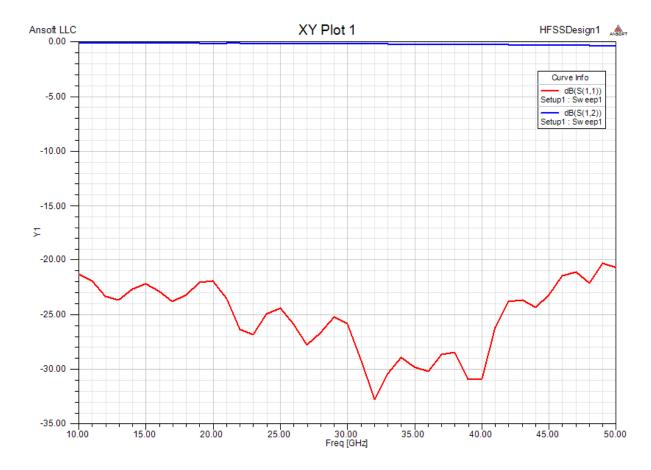

Al analizar los problemas descritos, se identificó que el elemento común en ambos módulos son los conectores 2.4 mm que se utilizan a la entrada y salida de ambos módulos. Se encontró que el montaje de estos conectores, que corresponde a un agujero recto en la pared del bloque de montaje, no es la más idónea. Como alternativa, se estudia un diseño que corresponde a un agujero cuyo radio varía de forma escalonada, llamado montaje de adaptación. Las simulaciones indican que las reflexiones son menores a  $-20 \ dB$ , lo que representa mejores resultados que el montaje simple.

En conclusión, este trabajo ha permitido identificar problemas no previstos en la caracterización del transistor de prueba. Se espera que al cambiar el método de montaje de los conectores 2.4 mm el sistema diseñado funcione correctamente.

# Índice General

| 1. | $\mathbf{Intr}$          | oducci                                  | ón                                        | 8          |

|----|--------------------------|-----------------------------------------|-------------------------------------------|------------|

|    | 1.1.                     | .1. Antecedentes                        |                                           |            |

|    |                          | 1.1.1.                                  | Antecedentes Generales                    | 8          |

|    |                          | 1.1.2.                                  | Antecedentes Específicos                  | 10         |

|    | 1.2.                     | .2. Objetivos                           |                                           |            |

|    |                          | 1.2.1.                                  | Objetivos Generales                       | 11         |

|    |                          | 1.2.2.                                  | Objetivos Específicos                     | 12         |

|    | 1.3.                     | Estruc                                  | tura del Informe                          | 12         |

| 2. | Mar                      | co Teá                                  | órico                                     | <b>1</b> 4 |

|    | 2.1. Conceptos Generales |                                         | ptos Generales                            | 14         |

|    |                          | 2.1.1.                                  | Líneas Microstrip                         | 14         |

|    |                          | 2.1.2.                                  | Parámetros $S$                            | 15         |

|    |                          | 2.1.3.                                  | Carta Smith                               | 17         |

|    |                          | 2.1.4.                                  | Ruido                                     | 18         |

|    | 2.2.                     | Transi                                  | stores de Alta Movilidad Electrónica HEMT | 23         |

|    |                          | 2.2.1.                                  | Descripción y Funcionamiento              | 23         |

|    |                          | 2.2.2.                                  | Modelo equivalente                        | 24         |

|    | 2.3.                     | 3. Caracterización de Transistores HEMT |                                           |            |

|    |                          | 2.3.1.                                  | Obtención De Parámetros Extrínsecos       | 26         |

|    |                          | 2.3.2.                                  | Obtención de Parámetros Intrínsecos       | 27         |

|    | 2.4.                     | Calibra                                 | ación TRL                                 | 29         |

|            |               | 2.4.1.  | Grafos de Flujo de Señales               | 29         |  |

|------------|---------------|---------|------------------------------------------|------------|--|

|            |               | 2.4.2.  | Concepto de Calibración                  | 30         |  |

|            |               | 2.4.3.  | Calibración TRL                          | 31         |  |

| 3.         | Des           | arrollo |                                          | 36         |  |

|            | 3.1.          | Descri  | pción del Sistema de medición            | 36         |  |

|            | 3.2.          | Transi  | stor a Utilizar                          | 38         |  |

|            | 3.3. Bias Tee |         |                                          | 38         |  |

|            |               | 3.3.1.  | Diseño del Bias Tee                      | 40         |  |

|            |               | 3.3.2.  | Construcción de Componentes              | 46         |  |

|            |               | 3.3.3.  | Montaje del Bias Tee                     | 51         |  |

|            | 3.4.          | Bloque  | e del Transistor                         | 54         |  |

|            | 3.5.          | Calibra | ación TRL                                | 57         |  |

|            |               | 3.5.1.  | Elección del Plano de Calibración        | 57         |  |

|            |               | 3.5.2.  | Diseño y construcción de Standards       | 58         |  |

|            |               | 3.5.3.  | Bloque de Calibración                    | 59         |  |

|            |               | 3.5.4.  | Incorporación de la Calibración al VNA   | 60         |  |

|            | 3.6.          | Protoc  | colo de Pruebas y Procesamiento de Datos | 62         |  |

|            |               | 3.6.1.  | Protocolo de Pruebas                     | 62         |  |

|            |               | 3.6.2.  | Procesamiento de Datos                   | 63         |  |

| 4.         | Res           | ultado  | s y Análisis                             | 64         |  |

|            | 4.1.          | Bias T  | 'ee                                      | 64         |  |

|            | 4.2.          | Calibra | ación TRL                                | 66         |  |

|            | 4.3.          | Anális  | is de conectores 2.4 mm                  | 70         |  |

| <b>5</b> . | Con           | clusio  | nes                                      | <b>7</b> 8 |  |

| Aı         | Anexos        |         |                                          |            |  |

| Re         | Referencias   |         |                                          |            |  |

# Índice de figuras

| 2.1.  | Geometria Línea Microstrip                                                      | 14 |

|-------|---------------------------------------------------------------------------------|----|

| 2.2.  | Campos en Línea Microstrip                                                      | 15 |

| 2.3.  | Circuito de dos puertos con ondas incidentes y reflejadas                       | 16 |

| 2.4.  | Significado físico de paramtetros $S.$                                          | 17 |

| 2.5.  | Gráfico Polar con coeficiente de reflexión para corto circuito, adaptación per- |    |

|       | fecta y circuito abierto                                                        | 18 |

| 2.6.  | Carta Smith círculos de igual resistencia                                       | 19 |

| 2.7.  | Carta Smith estándar                                                            | 20 |

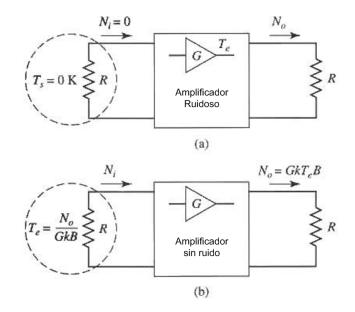

| 2.8.  | Ruido equivalente de un dispositivo de ganancia $G.$ $(a)$ Dispositivo ruidoso. |    |

|       | (b) Dispositivo sin ruido                                                       | 21 |

| 2.9.  | Ruido en circuito receptor formado por elementos ruidosos en cascada            | 21 |

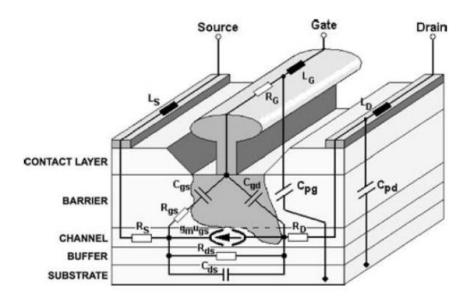

| 2.10. | Diagrama del Transistor HEMT                                                    | 23 |

| 2.11. | Principio de Modulación de Dopaje en HEMT                                       | 24 |

| 2.12. | Circuito equivalente de pequeña señal de un HEMT representado sobre el          |    |

|       | dispositivo físico.                                                             | 25 |

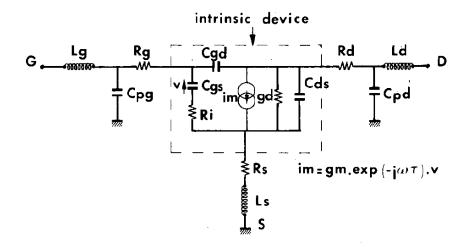

| 2.13. | Circuito equivalente de pequeña señal del transistor HEMT                       | 26 |

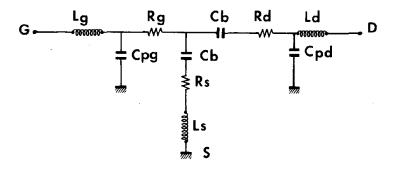

| 2.14. | Circuito equivalente de pequeña señal del transistor HEMT a $V_{gs}=0.$         | 26 |

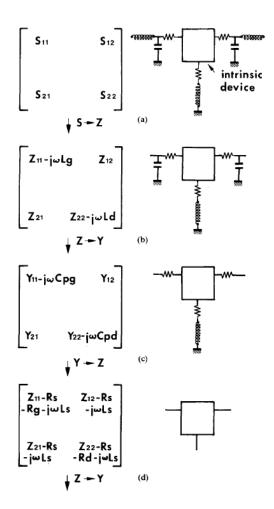

| 2.15. | Método para extraer la matriz $Y$ intrínseca del transistor                     | 28 |

| 2.16. | Representación en grafo de flujo de señales de una red dos puertos              | 30 |

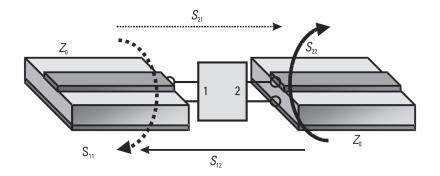

| 2.17. | Diagrama de Bloques de medición en VNA de un dispositivo de dos puertos.        | 31 |

| 2.18. | Diagrama de Bloques Calibración TRL                                             | 32 |

| 2.19. | Diagrama de Bloques y grafos de flujos de señales de standards de calibración        |    |

|-------|--------------------------------------------------------------------------------------|----|

|       | TRL. (a) Throu. (b) Reflect. (c) Line                                                | 35 |

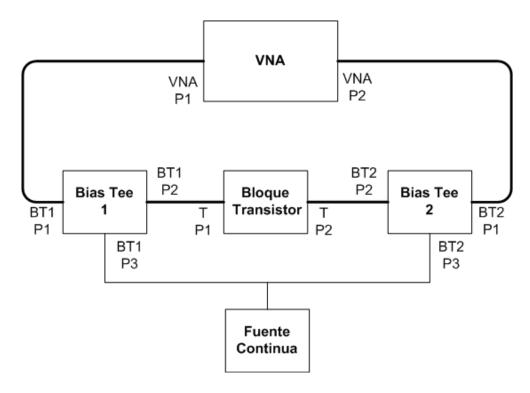

| 3.1.  | Diagrama de conexión del sistema de medición.                                        | 37 |

| 3.2.  | Conectores. (a) 2.4 mm macho. (b) 2.4 mm hembra. (c) SMA hembra                      | 38 |

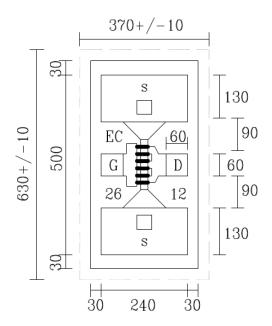

| 3.3.  | Esquema de transistor p<br>Hem<br>t EC2612 con dimensiones físicas en $\mu m.$       | 39 |

| 3.4.  | Diagrama de bloques del filtro Bias Tee                                              | 40 |

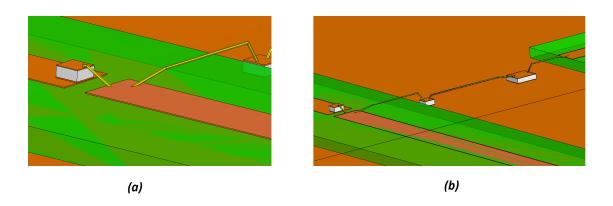

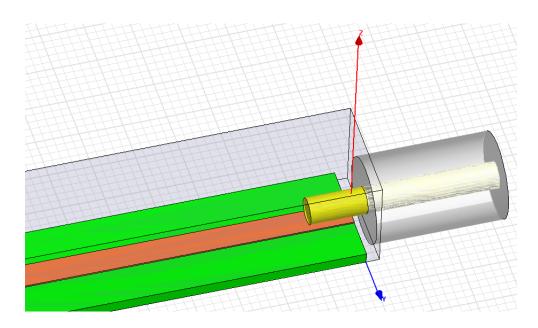

| 3.5.  | Renderización del modelo en HFSS del Bias Tee                                        | 41 |

| 3.6.  | Renderización de los Filtros del Bias Tee en mayor detalle. $(a)$ Filtro pasa        |    |

|       | altos. $(b)$ Filtro pasa bajos                                                       | 42 |

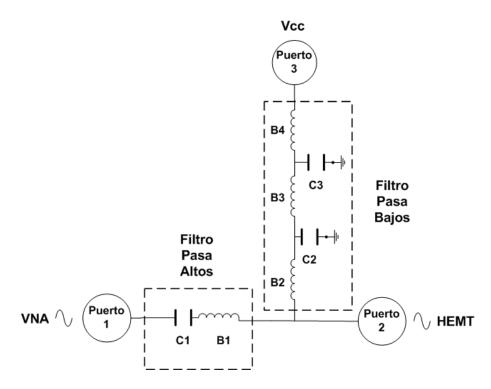

| 3.7.  | Diagrama circuital del Bias Tee                                                      | 43 |

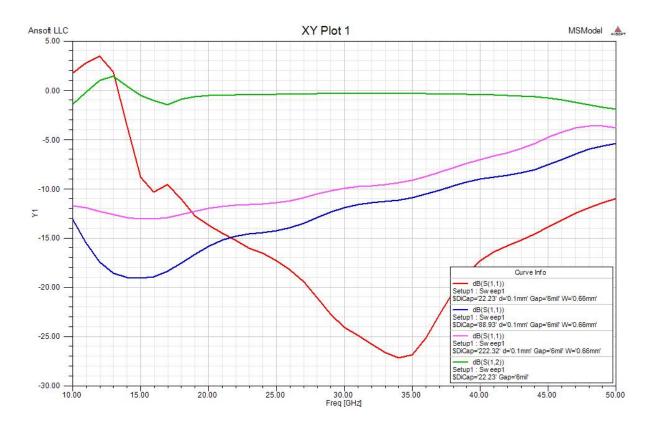

| 3.8.  | Simulación de Bias Tee en HFSS, con $gap$ de 6 $mil$ , para valore de $C_1$ de 0.1,  |    |

|       | 0.4 y 1 pF                                                                           | 45 |

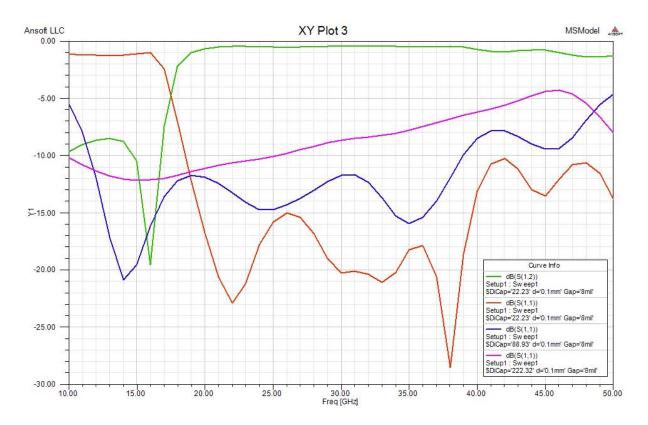

| 3.9.  | Simulación de Bias Tee en HFSS, con $gap$ de 8 $mil$ , para valore de $C_1$ de 0.1,  |    |

|       | 0.4 y 1 pF                                                                           | 46 |

| 3.10. | Simulación de Bias Tee en HFSS, con $gap$ de 10 $mil$ , para valore de $C_1$ de 0.1, |    |

|       | 0.4 y 1 pF                                                                           | 47 |

| 3.11. | Diagrama de montaje de conector en pared del bloque de duraluminio                   | 48 |

| 3.12. | Fotografía de las líneas microstrip fabricadas.                                      | 50 |

| 3.13. | Fotografía de las líneas microstrip montadas sobre el bloque de duraluminio.         | 53 |

| 3.14. | Fotografía de condensadores y líneas montados sobre el bloque de duraluminio.        | 55 |

| 3.15. | Diagrama que muestra el plano de calibración TRL en el bloque del transistor.        | 57 |

| 3.16. | Fotografía del bloque del sistema de calibración con un bloque removible acom-       |    |

|       | plado                                                                                | 59 |

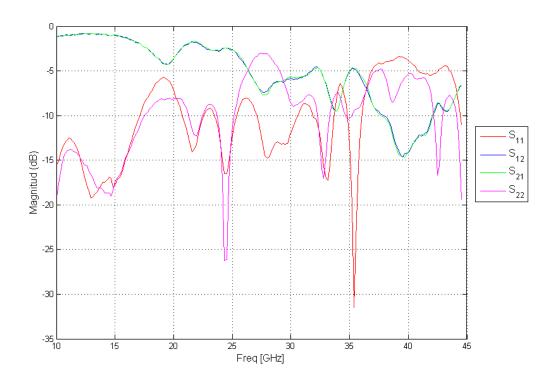

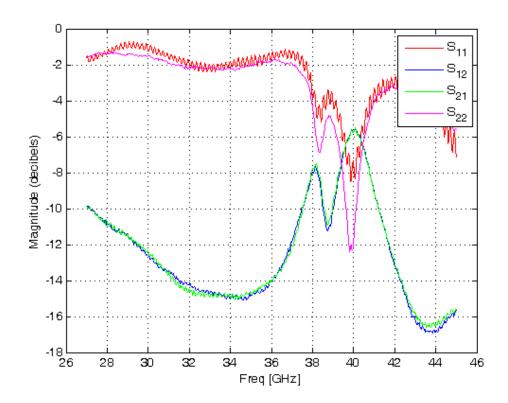

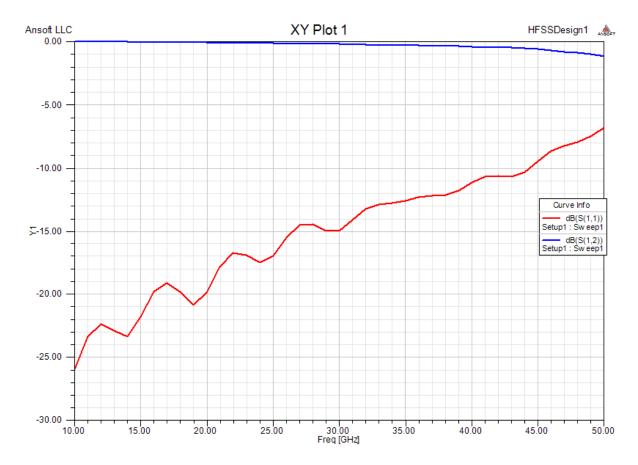

| 4.1.  | Gráfico de parámetros $S$ del Bias Tee. Conectores 2.4 mm                            | 65 |

| 4.2.  | Gráfico de parámetros $S$ de línea de 50 $\Omega.$ Conectores 2.4 mm                 | 66 |

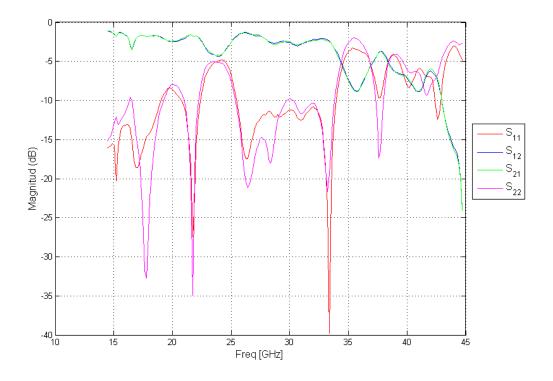

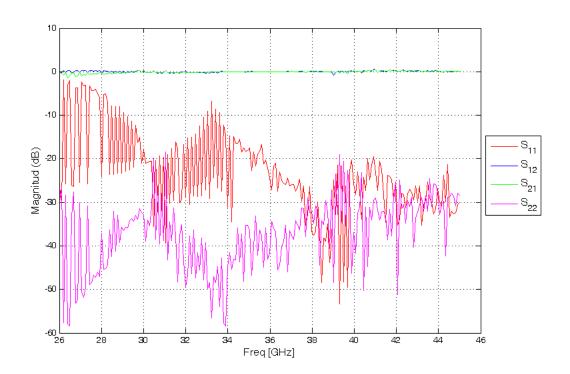

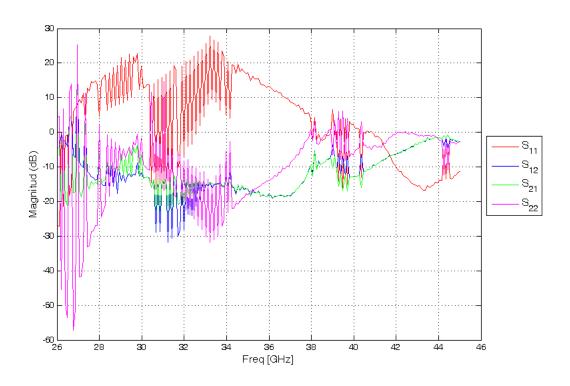

| 4.3.  | Gráfico de parámetros $S$ del $standard\ Thru$ bajo calibración estándar             | 67 |

| 4.4.  | Gráfico de parámetros S del standard Thru tras la calibración TRL                    | 68 |

| 4.5. | Gráfico de parámetros $S$ del $standard\ Thru$ tras la calibración TRL, al reco-           |    |

|------|--------------------------------------------------------------------------------------------|----|

|      | nectar el puerto 2                                                                         | 69 |

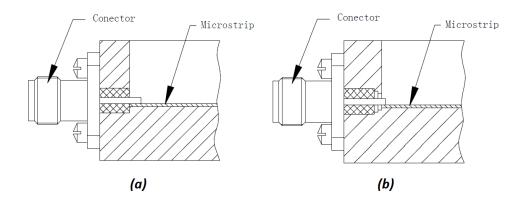

| 4.6. | Diagrama de montaje de conectores 2.4 mm. $(a)$ montaje simple. $(b)$ montaje              |    |

|      | de adaptación                                                                              | 70 |

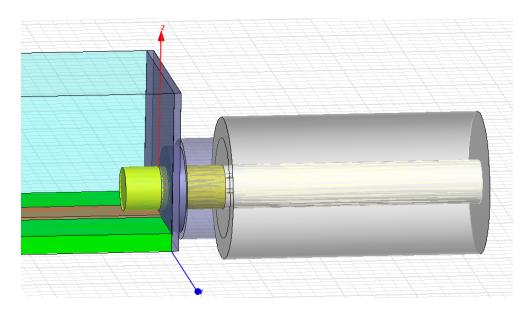

| 4.7. | Renderización del modelo en HFSS del conector 2.4 mm en configuración simple.              | 71 |

| 4.8. | Renderización del modelo en HFSS del conector 2.4 mm en configuración de                   |    |

|      | adaptación                                                                                 | 72 |

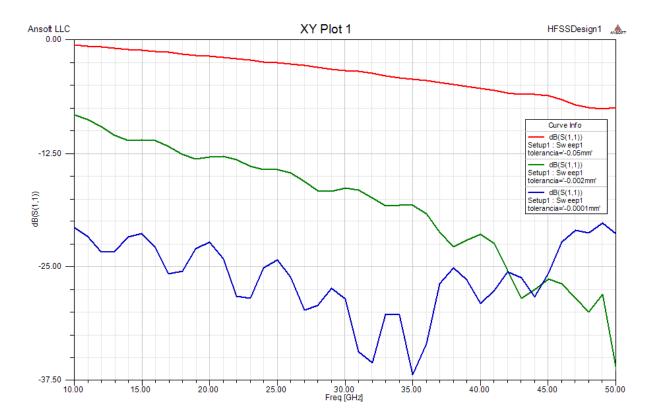

| 4.9. | Gráfico de parámetros $S$ de la simulación del conector $2.4~\mathrm{mm}$ en configuración |    |

|      | simple                                                                                     | 73 |

| 4.10 | . Gráfico de parámetros $S$ de la simulación del conector 2.4 mm en configuración          |    |

|      | de adaptación                                                                              | 74 |

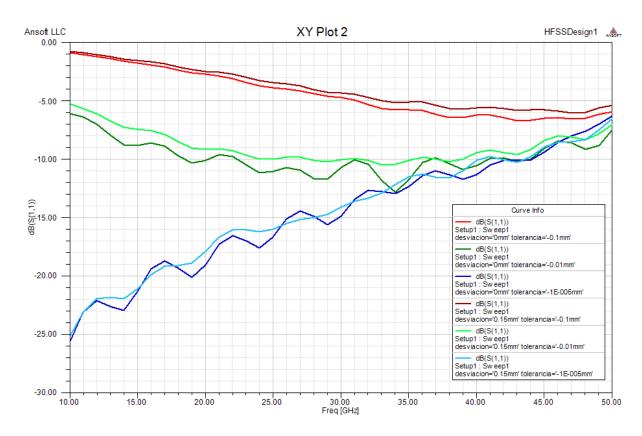

| 4.11 | . Gráfico de parámetros $S_{11}$ de la simulación del conector 2.4 mm en configu           |    |

|      | ración simple, ante variaciones de su alineamiento vertical y horizontal con               |    |

|      | respecto a la línea.                                                                       | 75 |

| 4.12 | . Gráfico de parámetros $S_{11}$ de la simulación del conector 2.4 mm en configura-        |    |

|      | ción de adaptación, ante variaciones de su alineamiento vertical con respecto              |    |

|      | a la línea                                                                                 | 76 |

# Capítulo 1

# Introducción

#### 1.1. Antecedentes

#### 1.1.1. Antecedentes Generales

La necesidad de conocer más, de ampliar el entendimiento del universo, de no conformarse con lo desconocido, es una de las características más definitorias del ser humano. El hombre no fue capaz de aceptar la simplicidad del ser, si no que se planteó dudas sobre la finalidad de su existencia, sobre como funciona el mundo a su alrededor, sobre las leyes que lo rigen y sobre lo que hay más allá de su entorno inmediato.

A medida que el hombre ganaba más conciencia sobre su entorno, empezó a generar mapas. en un principio fue por motivos prácticos, luego, el motivo cambió. Ya no sólo quería

referenciar recursos, como alimentos, agua y minerales, ahora buscaba expandir su mundo,

sus conocimientos y su entendimiento. Esto se puede ver en el descubrimiento de América. Si

bien los financiamientos y la aceptación mundial de la exploración estuvieron muy motivados

por las expectativas de ganancia económica, los primeros hombres, los que encendieron la

chispa del viaje, los que querían cambiar los preceptos sobre la morfología terráquea, estos

hombres tenían como motivación la más pura y desesperada sed de conocimiento, curiosidad

desbordada, que los llevo a promover, impulsar y gestar tales viajes.

Mucho antes que el descubrimiento de América, 6000 años antes o más, el hombre ya ex-

ploraba con la vista y construía mapas de la bóveda celeste. En la actualidad con la superficie terrestre ampliamente explorada, el hombre centra aun más su atención en espacio exterior, ya no quiere saber sólo donde se encuentran los objetos fuera del planeta, o donde se encuentra el planeta dentro del sistema, si no que quiere saber de que están compuestos y cómo se formaron, quiere saber si las leyes que rigen dentro del planeta son las mismas que rigen en el universo completo. Una evidencia de aquello es que en este momento se han establecido los proyectos para fabricar los observatorios astronómicos más grandes jamás realizados.

Las técnicas de observación utilizadas en la antigüedad han ido variado, al principio sólo se observaba hacia el cielo, se establecían un conjunto de puntos brillantes como referencia, y se mapeaba los astros referenciados a otros astros, observando que éstas podían ser usadas para orientarse en la Tierra. Con la invención del telescopio en el siglo XVII fue posible observar con más detalle el cielo, ir graduando la separación de estrellas y hacer un registro de sus órbitas. El telescopio fue evolucionando y aumentando de tamaño, hoy en día se tienen grandes construcciones que contienen precisos telescopios con varios espejos operando en conjunto. Las técnicas de observación se han ampliado, en la actualidad no sólo se tienen telescopios ópticos, sino que también, desde 1931 Gracias al descubrimiento de Jansky, radiotelescopios, que recibiendo ondas electromagnéticas puede conocer las partículas que las emitieron.

El Atacama Large Milimiter Array (ALMA), es el proyecto más grande de radioastronomía que ha existido y en este momento se construye en la región de Atacama de Chile. Éste consiste en un arreglo de 66 telescopios que trabajaran en conjunto para, por medio de interferometría, obtener mejor resolución de las ondas provenientes del espacio y así poder recibir ondas muy débiles de lugares muy lejanos del universo.

Las ondas provenientes de los lugares más lejanos del espacio varían significativamente su frecuencia en su viaje a la Tierra, esto se debe al efecto doppler. Las frecuencias de estas ondas disminuyen, por lo que se que tienen un alto corrimiento al rojo. En el proyecto ALMA, la banda donde se perciben estos objetos es llama banda 1, y corresponde a frecuencias entre los 30 y los 45 GHz.

### 1.1.2. Antecedentes Específicos

El Grupo de Instrumentación Astronómica perteneciente al Departamento de Ingeniería Eléctrica (DIE) y al Departamento de Astronomía (DAS) de la Facultad de Ciencias Físicas y Matemáticas de la Universidad de Chile, trabaja para proveer al proyecto ALMA de receptores de antenas que capten ondas electromagnéticas en banda 1 (30-45 Ghz). Dado que las señales que se captan son de muy baja intensidad, es necesario aplicar varias etapas de amplificación en el receptor para asegurar que la señal no se pierda por el ruido que se produce en la etapa de recepción. Para cumplir con estos objetivos de amplificación, ALMA ha establecido criterios muy estrictos en cuanto al ruido aceptado en estas etapas. Así, los amplificadores de bajo ruido que se encuentran en el mercado no satisfacen todos lo requerimientos del proyecto, lo que propende al Grupo de Instrumentación Astronómica a buscar soluciones no comerciales a este problema.

Ante estas condiciones, el Grupo de Instrumentación Astronómica experimenta con distintas soluciones, entre las que se cuentan: realizar pruebas de montaje de amplificadores para reducir el ruido que pueda añadir este proceso, probar distintos tipos de tecnologías de amplificación de bajo ruido utilizando soluciones comerciales avanzadas y fabricar amplificadores de bajo ruido que cumplan con los requerimientos. Dentro de este último enfoque, las dos tareas principales son: encontrar un diseño de amplificador adecuado y encontrar los elementos óptimos para construir el diseño. Dado que el elemento que más influye en el ruido de un amplificador es el transistor, es en estos semiconductores donde esta el foco de diseño. El examinar distintas tecnologías permitirá establecer que tipo de transistores son los más apropiados para los requerimientos, para esto se requiere conocer el modelo de circuito

equivalente de cada transistor a utilizar a modo de simular y establecer comparaciones entre distintos dispositivos.

Es imperativo entonces, tener una metodología de caracterización de transistores que permita tener mediciones propias del comportamiento de estos dispositivos. Esto por un lado para no depender de los datasheet del fabricante y por otro lado para trabajar con semiconductores que no han sido medidos aún.

En esta memoria se documentara el proceso de diseño y construir un sistema de caracterización enfocado en transistores HEMT, acotado entre 30 y 50 Ghz. Este sistema estará basado en líneas microstrip montadas en bloques de aluminio, interconectados por cable coaxial. El sistema de caracterización estará compuesto por el bloque donde estará montado el transistor; un Vector Network Analyser (VNA) para realizar las mediciones; un par de filtros Bias Tee que permiten ingresar la señal y la polarización al transistor por un mismo canal; un sistema de calibración TRL que permitirá descontar los errores introducidos al medir el transistor por las etapas que conectan a éste con el VNA, tales como cables, conectores, adaptadores y Bias Tee; y un sofware que a partir de los parámetros S obtenidos, calculara el modelo equivalente del transistor.

# 1.2. Objetivos

# 1.2.1. Objetivos Generales

- Dotar las antenas del proyecto ALMA de la instrumentación necesaria para operar.

- Diseñar y construir receptores de antena para cada una de las 10 bandas del proyecto ALMA.

- Desarrollar un prototipo de receptor de banda 1 para antenas del proyecto ALMA, que cumpla con las especificaciones establecidas.

- Probar distintos amplificadores que puedan ser utilizados en el receptor.

- Construir un amplificador basado en tecnología HEMT que pueda ser utilizado en el receptor.

- Examinar distintos transistores HEMT, y comprobar la factibilidad de utilizarlos para fabricar el amplificador mencionado.

### 1.2.2. Objetivos Específicos

- Caracterizar distintos transistores HEMT.

- Establecer y construir un método de pruebas, y desarrollo de datos que permita caracterizar transistores HEMT.

- Establecer protocolo de pruebas.

- Diseñar y construir infraestructura de pruebas.

- Diseñar y construir filtros Bias Tee que permitan juntar la polarización proveniente de la fuente y las señales pequeñas provenientes del VNA para que lleguen al transistor por el mismo canal Microstrip.

- Realizar un programa en MATLAB que procese los datos de las pruebas y entregue el circuito equivalente del transistor medido.

## 1.3. Estructura del Informe

En el capitulo 1 se puede leer la introducción y objetivos de la memoria que la contextualizan al tiempo que lo describen brevemente. El capitulo 2 explica los conceptos más importantes utilizados en el documento, al tiempo que expone la teoría detrás del sistema de calibración. El capitulo 3 se encarga de detallar el proceso de diseño y construcción de cada uno de los elementos del sistema. El capitulo 4 muestra los resultados obtenidos. Finalmente,

el capitulo 5 expone las conclusiones del trabajo realizado, discutiendo los temas que quedaron inconclusos, que pueden ser mejorados, y líneas de trabajo futuras.

# Capítulo 2

# Marco Teórico

# 2.1. Conceptos Generales

### 2.1.1. Líneas Microstrip

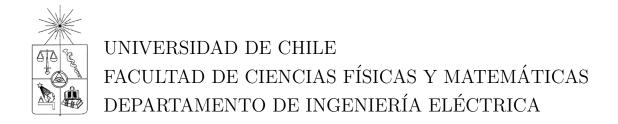

La línea microstrip es una de las líneas de transmisión plana más utilizadas, básicamente por que es fácil de fabricar usando fotolitografía a la vez que es fácil de integrar con otros elementos microondas. Como se puede ver en la figura 2.1, una línea microstrip está compuesta por un conductor de ancho W impreso en un dieléctrico delgado de altura d. La superficie contraria a donde se ubica el conductor en el dieléctrico está cubierto por una placa metálica que constituye la tierra.

Figura 2.1: Geometria Línea Microstrip.

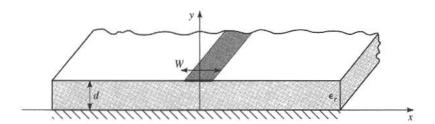

Si bien la mayoría de las líneas de campo en una línea microstrip se concentran en el dieléctrico, como se ve en la figura 2.2, algunas utilizan el aire como medio. Dado que ambos

medios tiene distintas velocidades de fase, no se puede formar un modo TEM en esta geometría. El comportamiento, es de hecho, un híbrido TM-TE pero dado que el dieléctrico es muy delgado, se comporta como un modo cuasi-TEM. Así la velocidad de fase y la constante de propagación se puede expresar de la siguiente manera [1].

$$v_p = \frac{C}{\sqrt{\epsilon_e}} \tag{2.1}$$

$$\beta = K_0 \sqrt{\epsilon_e} \tag{2.2}$$

Figura 2.2: Campos en Línea Microstrip.

#### 2.1.2. Parámetros S

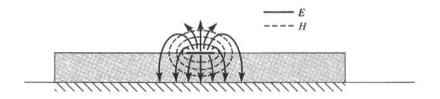

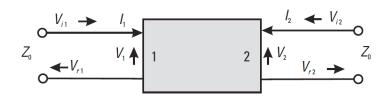

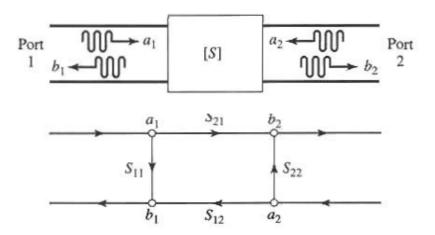

Los Parámetros S o Parámetros de Scattering (dispersión), es una forma de representar un circuito en términos de que cantidad de una señal se dispersa cuando incide en el circuito. La representación de un circuito en parametros S se llama matriz de scattering o matriz S. La figura 2.3 representa un circuito de dos puertos, donde  $V_{i1}$  y  $V_{r1}$  representan respectivamente, los voltajes de las ondas incidente y reflejada en el puerto 1,  $V_{i2}$  y  $V_{r2}$ , los voltajes de las ondas incidente y reflejada en el puerto 2. La potencia que incide en el puerto 1 dada por la ecuación 2.3 puede ser usada para definir una nueva variable  $a_1$ , de la misma forma la potencia reflejada en el puerto 2 puede ser usada para definir  $b_1$  en la ecuación 2.4, y de la misma manera se definen  $a_2$  y  $b_2$  en el puerto 2. Con ésto se puede obtener el voltaje y la corriente total en el puerto 1 dado por las ecuaciones 2.5 y 2.6 [2].

$$P_{incidente}(1) = \frac{|V_{i1}|^2}{Z_0} = |a_1|^2 \tag{2.3}$$

$$P_{reflejada}(1) = \frac{|V_{r1}|^2}{Z_0} = |b_1|^2 \tag{2.4}$$

$$V_1 = \sqrt{Z_0}(a_1 + b_1) \tag{2.5}$$

$$I_1 = \frac{(a_1 - b_1)}{\sqrt{Z_0}} \tag{2.6}$$

Figura 2.3: Circuito de dos puertos con ondas incidentes y reflejadas.

Luego acudiendo a las mismas ecuaciones para el puerto 2, y resolviendo el sistema dejando  $b_1$  y  $b_2$  como variables dependientes, y  $a_1$  y  $a_2$  como variables independientes, se obtiene la matriz de scattering para un circuito de dos puertos dada por 2.7.

$$\begin{bmatrix} b_1 \\ b_2 \end{bmatrix} = \begin{bmatrix} S_{11} & S_{12} \\ S_{21} & S_{22} \end{bmatrix} \begin{bmatrix} a_1 \\ a_2 \end{bmatrix}$$

$$(2.7)$$

Los elementos de la matriz S tiene significado físico:  $S_{ij}$  corresponde a la amplitud y fase del voltaje de la señal de salida en el puerto i con respecto al voltaje de la señal de entrada en el puerto j;  $S_{ii}$  corresponde al voltaje de la señal de salida del puerto i con respecto al voltaje de la señal de entrada del puerto i. En terminos más simples,  $S_{ij}$  representa la cantidad de señal transmitida del puerto j al puerto i, mientras que  $S_{ii}$  representa la cantidad de señal reflejada por el puerto i. Ésto se puede ver en el caso de un circuito de 2 puertos en la figura 2.4.

Figura 2.4: Significado físico de paramtetros S.

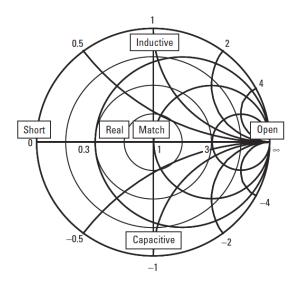

#### 2.1.3. Carta Smith

La carta smith es un método gráfico que sirve no sólo para representar impedancias y coeficientes de reflexión, si no que para transformar gráficamente entre éstos. Su característica principal es ser capaz de mostrar todos los posibles coeficientes de reflexión, impedancias y admitancias de un circuito pasivo en un gráfico finito.

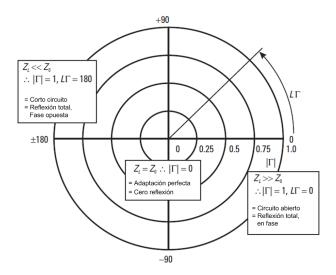

Si se considera una línea de impedancia  $Z_0$  terminada en una carga de impedancia  $Z_L$ , el coeficiente de reflexión  $\Gamma$  dado por la ecuación 2.8 sera un valor complejo que puede ser representado en un gráfico polar, como muestra la figura 2.5. Se puede ver en la ecuación 2.8 que si la carga se adapta totalmente a la línea, se tendrá un punto en el centro de la carta smith para representar a  $Z_L$ , si la carga es un cortocircuito entonces se tendrá un punto dibujado al extremo izquierdo del gráfico, y si es un circuito abierto, se tendrá un punto en el lado derecho. Los circulos concentricos representan líneas de igual magnitud de coeficiente de reflexión.

$$\Gamma = (Z_L - Z_0)/(Z_L + Z_0) \tag{2.8}$$

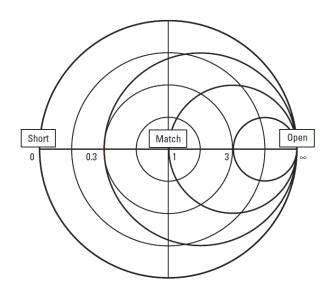

La carta smith contiene ademas círculos de igual resistencia normalizada, las que tienen un lado adyacente al extremo derecho del diagrama smith que representa el circuito abierto

Figura 2.5: Gráfico Polar con coeficiente de reflexión para corto circuito, adaptación perfecta y circuito abierto.

de impedancia infinita, el cortocircuito esta al extremo izquierdo, y la adaptación perfecta corresponde al centro del diagrama smith, como se puede ver en la figura 2.6. De la misma forma se pueden graficar círculos de igual admitancia que serán adyacentes al lado izquierdo de la carta smith. En la figura 2.7 se puede ver una carta smith estándar que incluye las líneas de igual reactancia, que van desde los bordes del diagrama hacia el punto de circuito abierto [2].

#### 2.1.4. Ruido

El ruido afecta de manera significativa los sistemas de recepción en microondas, definiendo el nivel más débil de señal que podrá ser capturado. Hay dos fuentes de ruido en un sistema de recepción, el ruido captado por la antena y el ruido intrínseco del circuito receptor. El primero se compone por todas las fuentes de ruido que llegan a la antena junto con la señal de interés, tales como los astros cercanos como el Sol y la Luna, las distintas capas de la atmósfera terrestre y tormentas cósmicas entre otras. El ruido intrínseco de un circuito se debe al movimiento aleatorio de electrones en un material debido a la temperatura de éste. El ruido que ingresa por la antena se amplifica o pierde en la misma proporción que la señal

Figura 2.6: Carta Smith círculos de igual resistencia.

de interés al pasar por el circuito receptor, por lo que la relación señal ruido de la antena no puede ser modificada por el receptor. La mejor forma de tratarlo es haciendo un diseño eficiente de antena y eligiendo un buen lugar donde colocarla. El ruido intrínseco del circuito receptor se ira sumando al ruido de entrada deteriorando la relación señal-ruido dentro del receptor. La forma de tratarlo es utilizando en la primera etapa de recepción un amplificador de bajo ruido.

#### Potencia de Ruido

La potencia de ruido efectiva n [W] generada por un dispositivo es directamente proporcional a la temperatura física T [K] y el ancho de banda de ruido considerado  $B_n$  [Hz], como se ve en la ecuación 2.9. En el caso que el elemento aplique una amplificación o disipación de la señal de entrada a la salida, esta formula cambia a 2.10, donde G representa la ganancia o perdida del elemento.

$$n = kTB_n[W] (2.9)$$

Figura 2.7: Carta Smith estándar.

$$n = GkTB_n[W] (2.10)$$

Donde  $k=1,379\times 10^{-23}[W/HzK]$  es la constante de boltzmann.

#### Temperatura de Ruido Equivalente

A un componente ruidoso que genera una temperatura de ruido  $N_0$  a su salida como el que se ve en la figura 2.8 (a), se le puede definir una temperatura de ruido equivalente  $T_e$ , que aplicada a la resistencia de fuente a la entrada del dispositivo, genera la misma potencia de ruido  $N_0$  a la salida del este. El dispositivo en este caso se considera sin ruido como aparece en la figura 2.8 (b).  $T_e$  esta dada por la ecuación 2.11.

$$T_e = \frac{N_0}{GkB}[K] \tag{2.11}$$

**Figura 2.8:** Ruido equivalente de un dispositivo de ganancia G. (a) Dispositivo ruidoso. (b) Dispositivo sin ruido.

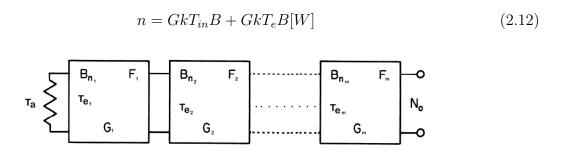

#### Ruido en Circuito en Cascada

Si la entrada de un dispositivo ruidoso de temperatura de ruido equivalente  $T_e$  y ganancia G, esta conectada a una fuente de ruido con temperatura de ruido equivalente  $T_{in}$ , la potencia de ruido a la salida estará dada por la ecuación 2.12.

Figura 2.9: Ruido en circuito receptor formado por elementos ruidosos en cascada.

Ahora se analizará un circuito formado por elementos en cascada, con una fuente de ruido conectada a la entrada, tomando como ejemplo un sistema de recepción. En este caso el cir-

cuito en cascada representa el circuito receptor y la fuente de ruido a la entrada representa el ruido proveniente de la antena. Este circuito se ve en la figura 2.9, donde  $T_a$  es la temperatura equivalente de ruido de la antena a la entrada del circuito receptor,  $G_i$  es la ganancia de la etapa i,  $B_i$  es el ancho de banda de cada etapa, y  $T_{e_i}$  es la temperatura de ruido equivalente de la etapa i. El ruido a la salida del sistema  $N_0$  esta dado por la ecuación 2.13, donde  $T_e$  representa la temperatura de ruido equivalente del sistema completo dado por la ecuación 2.14, donde  $T_r$  representa la temperatura de ruido del circuito receptor dado por la ecuación 2.15.

$$N_0 = \prod_{i=1}^{m} G_i k T_e (2.13)$$

$$T_e = T_a + T_r \tag{2.14}$$

$$T_r = T_{e_1} + \frac{T_{e_2}}{G_1} + \frac{T_{e_3}}{G_1 G_2} + \dots + \frac{T_{e_m}}{\prod_{i=1}^{m-1} G_i}$$

(2.15)

Como se puede ver en las ecuaciones 2.14 y 2.15 la temperatura equivalente del sistema esta dada principalmente por el ruido de la antena y el ruido intrínseco de la primera etapa del circuito receptor, ya que el ruido de la segunda etapa se ve disminuido por la ganancia de la primera etapa, y el ruido de la tercera etapa se ve disminuido por las ganancias de la primera y segunda etapa. De este modo, los mejores esfuerzos en diseñar una etapa de buena ganancia y bajo ruido deben estar enfocados en la primera etapa, donde se obtendrá un beneficio mayor, mientras que las ultimas etapas no son preponderantes en el ruido del sistema [1].

### 2.2. Transistores de Alta Movilidad Electrónica HEMT

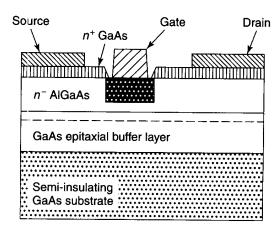

## 2.2.1. Descripción y Funcionamiento

El Transistor de Alta Movilidad Electrónica o HEMT (High Electron Mobility Transistor) es una tecnología de transistores desarrollada para operar con longitudes de onda milimétricas. Sus características principales son operar a alta frecuencia, hasta el orden de 100 GHz, y su bajo ruido, por lo que es muy utilizado en LNA (Low Noise Amplifiers). Su funcionamiento esta basado en el Transistor de Efecto de Campo o FET (Fild Effect Transistor), con la particularidad de que el canal de conducción en vez de formarse en el substrato, se forma entre dos capas de material con distinta banda prohibida (bandgap) formando entra ambos una heterounión (heterojunction), por lo que es también llamado HFET (Heterostructure FET). En la figura 2.10 se puede ver como se estructura un HEMT.

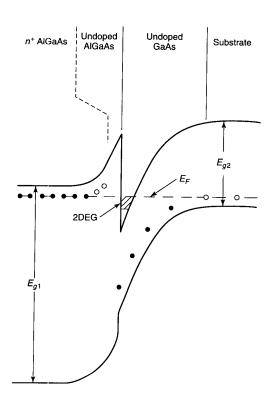

Al tener  $n^-$ AlGaAs un bandgap mayor a GaAs, se produce un pozo cuántico (Quantum Well) en la banda de conducción de la heterounión. Los electrones de  $n^-$ AlGaAs se difunden en el pozo cuántico generando un gas de dos dimensiones confinado en la juntura, en este gas los electrones tiene gran movilidad, lo que provoca que al ser utilizado como canal, el gas produce un transistor de alta frecuencia y muy bajo ruido.

Figura 2.10: Diagrama del Transistor HEMT.

La Generacion de este gas se debe al principio de dopaje modulado (Modulation Doping Principle), donde las cargas libres de una región altamente dopada se difunden en una región menormente dopada, donde son capaces de moverse con gran movilidad por el menor efecto del scattering debido a las impurezas, las que son menores en la región menormente dopada. En la figura 2.11 se puede ver como se forma el gas en dos dimensiones entre los dos materiales en un transistor HEMT, donde 2DEG representa al gas de dos grados de libertad [1], [3].

Figura 2.11: Principio de Modulación de Dopaje en HEMT.

#### 2.2.2. Modelo equivalente

Los parámetros del modelo equivalente de pequeña señal de un transistor, pueden ser divididos en dos grupos, los extrínsecos y los intrínsecos. El modelo de un transistor HEMT puede ser visto en la figura 2.13 donde se muestran ambos grupos de parámetros. En la figura 2.12 se pueden ver estos parámetros representados sobre el dispositivo físico.

Figura 2.12: Circuito equivalente de pequeña señal de un HEMT representado sobre el dispositivo físico.

Los parámetros extrínsecos son independientes de la polarización del dispositivo, y dan cuenta de los fenómenos físicos que se manifiestan en las capas más externas del transistor. Las inductancias parásitas  $L_s$ ,  $L_g$  y  $L_d$  representan respectivamente el efecto de inducción que se produce debido al contacto metálico de los pads en Source, Gate y Drain, las resistencias parásitas  $R_s$  y  $R_d$  representan la resistencia debido a los contactos ohmicos y  $R_g$  representa la resistencia de metalización,  $C_{pg}$  representa la capacitancia que se produce entre el pad del Gate y tierra, y  $C_{pd}$  la que se genera entre Drain y tierra.

Los parámetros intrínsecos dan cuenta de los fenómenos físicos en el interior del transistor, por lo que están ligados con el funcionamiento de éste, siendo dependientes de la polarización del dispositivo.  $C_{gs}$  y  $C_{gd}$  son debido a cargas de deplexión y  $C_{ds}$  es la capacitacia geométrica entre Drain y Source;  $g_m$  y  $g_d$  son transconductancias vinculadas a las corrientes al interior del dispositivo;  $\tau$  es el desface de la transconductancia, dado que la corriente no responde inmediatamente a los cambios de voltaje del Gate;  $R_i$  de cuestionable representación física fue introducido para mejor el modelo dado los valores de  $S_{11}$  [4], [5].

Figura 2.13: Circuito equivalente de pequeña señal del transistor HEMT.

### 2.3. Caracterización de Transistores HEMT

Existen diferentes métodos para obtener el modelo equivalente de señal pequeña de un transistor HEMT. El utilizado en este trabajo esta basado en [4], que consiste en medir los parámetros S del transistor bajo la condición  $V_{ds} = 0$  para medir los parámetros extrínsecos, aprovechando su independencia de la polarización. Luego estos parámetros son excluidos de la matriz S medida bajo polarización operacional, mediante un calculo de deembed para que ésta represente sólo al modelo intrínseco.

#### 2.3.1. Obtención De Parámetros Extrínsecos

Figura 2.14: Circuito equivalente de pequeña señal del transistor HEMT a  $V_{gs}=0.$

En la figura 2.14 se puede ver el modelo equivalente del transistor bajo condiciones de  $V_{ds} = 0$ , donde  $Z_{ij}$  esta representada por las ecuaciones 2.16, 2.17 y 2.18.

$$Z_{11} = R_s + R_g + \frac{R_c}{3} + \frac{nkT}{qI_q} + j\omega(L_s + L_g)$$

(2.16)

$$Z_{12} = Z_{21} = R_s + R_c/2 + j\omega L_s \tag{2.17}$$

$$Z_{22} = R_s + R_d + R_c + j\omega(L_s + L_d)$$

(2.18)

Donde  $R_c$  es la resistencia de canal bajo el Gate, n es el factor de idealidad, k la constante de Boltzmann, T la temperatura e  $I_g$  la corriente del Gate.

De las expresiones anteriores se puede ver que la parte real de Z es independiente de la frecuencia, mientras que la parte imaginaria varia linealmente con esta. Luego se pueden obtener los parámetros resistivos aplicando parte real a las expresiones anteriores, y los inductivos aplicando parte imaginaria a estas.

Para obtener los valores de resistencias del circuito equivalente se debe medir  $I_g$ , y realizar el gráfico  $Re(Z_{11})$  vs  $1/I_g$ . Ademas una relación adicional deber ser utilizada para encontrar  $R_c$ . Ésto no es problema por que existe redundancia de ecuaciones para resolver el sistema, que pueden ser encontradas en las referencias [5], [6] y [7] de [paper1]. Pero en la practica se pueden despreciar los términos  $R_c$  y  $\frac{nkT}{qI_g}$  de modo que los cálculos sean más directos. Para obtener los parámetros se las inductancias, conviene utilizar la segundo derivada numérica de las partes imaginarias.

#### 2.3.2. Obtención de Parámetros Intrínsecos

Con los parámetros extrínsecos ya obtenidos, se procede a polarizar de forma operacional, con lo que se obtendrá una matriz S de todo el transistor. Luego se realiza el deembed de los

parámetros extrínsecos. Para esto conviene trabajar con la matriz Y, debido a la topologia  $\pi$  del dispositivo.

Figura 2.15: Método para extraer la matriz Y intrínseca del transistor.

En la figura 2.15 se ven los pasos que hay que aplicar a la matriz S medida, para aplicar el deembeding de los parámetros extrínsecos, y obtener la matriz Y resultante que representa los parámetros intrínsecos. Los pasos son:

- 1. Medir los parámetros S del dispositivo

- 2. Transformar Sa Zy restar  $L_g$ y  $L_d$ que son elementos serie

- 3. Transformar Z a Y y restar  $C_{pg}$  y  $C_{pd}$  que están en paralelo

- 4. Transformar Y a Z y restar  $R_g$ ,  $R_s$ ,  $L_s$  y  $R_d$  que estan en serie

- 5. Transformar Z a Y que corresponde a la matriz Y de los elementos intrínsecos

La matriz Y del circuito intrínseco del transistor puede escribirse como 2.19, 2.20, 2.21 y 2.22. De estas ecuaciones se pueden calcular los parámetros intrínsecos.

$$Y_{11} = R_i C_{qs}^2 \omega^2 + j\omega (C_{qs} + C_{qd})$$

(2.19)

$$Y_{12} = -j\omega C_{gd} \tag{2.20}$$

$$Y_{21} = g_m - j\omega(C_{qd} + g_m(R_iC_{qs} + \tau))$$

(2.21)

$$Y_{22} = g_d + j\omega(C_{ds} + C_{gd}) (2.22)$$

De esta forma se ha obtenido la caracterización completa del transistor. Dado que los parámetros intrínsecos dependen de la polarización, este ultima etapa de la caracterización deber ser repetida para varios punto de operación en que se quiera conocer el circuito equivalente del dispositivo, y obtener curvas de estos dependientes de la polarización.

### 2.4. Calibración TRL

# 2.4.1. Grafos de Flujo de Señales

Los grafos de flujos de señales son la base de la calibración TRL, por lo que es necesario mencionarlos. Éstos son una técnica para representar redes de microonda por medio de ondas transmitidas y reflejadas. Cada puerto de la red es representado por dos nodos en el grafo,

donde uno se identifica con las ondas que entran al puerto, mientras que el otro con las ondas reflejadas en el puerto. El voltaje en cada nodo esta dado por la suma de las señales que ingresan en el. Los nodos están unidos por aristas con sentido, que representan el flujo de señales entre los nodos. Cada arista tiene relacionado un parámetro S o un coeficiente de reflexión. De esta forma una red de dos puertos puede ser presentada por un grafo de flujo de señales como se ve en la figura 2.16, donde por ejemplo una onda de voltaje  $a_1$  que incide en el puerto 1, se divide entre una onda onda trasmitida hacia el puerto 2 por  $S_{21}$  y una onda reflejada a través de  $S_{11}$ .

Figura 2.16: Representación en grafo de flujo de señales de una red dos puertos.

# 2.4.2. Concepto de Calibración

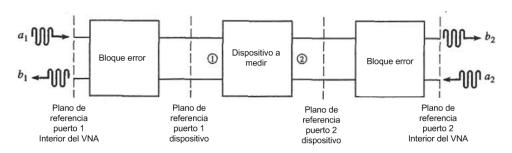

La caracterización de un circuito por medio de su medición se logra utilizando un Vector Network Analyzer (VNA), equipo que utiliza voltajes complejos, midiendo magnitud y fase de las señales, para obtener los parámetros S del circuito objetivo.

Un problema aparece al realizar estas mediciones debido a que el plano de referencia de los voltajes se encuentra al interior del VNA, por lo que cualquier medición incluirá las perdidas y desfases producidos por los cables, conectores y adaptadores que conectan el dispositivo a

medir (DAM) con el VNA. Ésto puede ser visto como el diagrama de bloques de la figura 2.17 donde un bloque representa al DAM, que esta conectado al VNA por medio de dos bloques de error que representan los elementos que conectan al DAM con cada puerto.

Figura 2.17: Diagrama de Bloques de medición en VNA de un dispositivo de dos puertos.

Hay una forma de extraer estos errores de la medición. El concepto de calibración consiste en caracterizar los bloques de error, para ser posteriormente restados matemáticamente a las mediciones del conjunto entero y así obtener los parámetros S del DAM aislado de errores. Las mediciones corregidas tendrán sus voltajes medidos con respecto a un nuevo plano de referencia llamado plano de calibración, el que se posiciona entre los dos bloques de error.

La forma mas simple de calibración es reemplazar el DAM por cargas conocidas llamadas standards, tales como cortocircuito, circuito abierto, o cargas bien adaptadas. Estos standards tienen parámetros S conocidos, de modo que se pueden ingresar manualmente al VNA para ser restados de la medición y de esta forma se puede obtener los parámetros S de los bloques de error. El problema con esta calibración es que estos standards son siempre imperfectos en cierto grado por lo que producen errores en la medición. Estos errores aumentan a frecuencias mayores, y a medida que se busca una medición de mayor calidad.

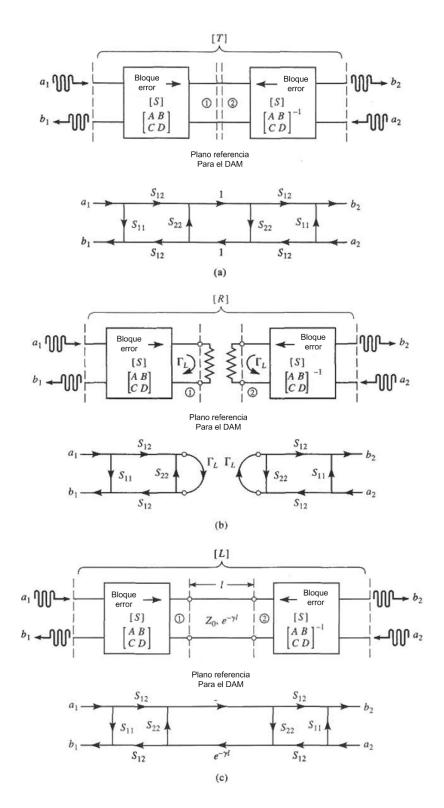

#### 2.4.3. Calibración TRL

La calibración TRL no depende de standards conocidos por lo que el error introducido entre los parámetros ideales ingresados al VNA y los parámetros reales de cada standard

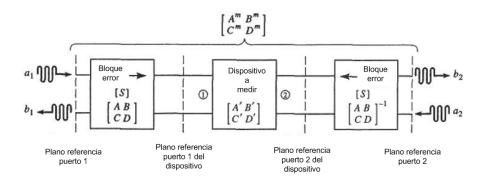

desaparecen. Utiliza tres simples conexiones Throu, Reflect y Line, que unen los bloques de error y permiten su caracterización sin tener que conocer por completo estos standards. La conexión Throu se logra conecta directamente los puertos en el plano de referencia deseado. Reflect se logra conectando una carga con alto indice de reflexión  $\Gamma_L$  a cada puerto. Estas cargas pueden ser un circuito abierto o un cortocircuito. Line consiste en conectar los puertos 1 y 2 a través de una línea de de la misma impedancia del sistema.

Figura 2.18: Diagrama de Bloques Calibración TRL.

El diagrama de bloques de la calibración TRL se ve en la figura 2.18. Se asume simetría entre los circuitos que conectan el VNA al DAM por cada puerto. De esta forma se obtiene dos relaciones, una es  $S_{21} = S_{12}$ , y la otra es la reciprocidad de las matrices ABCD de los bloques de error. Las matrices S de Throu, Reflect y Line serán llamadas respectivamente [T],[R] y [L].

Al insertar el Throu entre los planos de calibración se obtiene el diagrama de bloques de la figura 2.19 (a), con su respectivo grafo de flujo de señales. Del grafo se obtienen las ecuaciones 2.23 y 2.24, mientras que de la simetría y reciprocidad se obtienen las ecuaciones 2.25 y 2.26.

$$T_{11} = S_{11} + \frac{S_{22}S_{12}^2}{1 - S_{22}^2} \tag{2.23}$$

$$T_{12} = \frac{S_{12}^2}{1 - S_{22}^2} \tag{2.24}$$

$$T_{22} = T_{11} (2.25)$$

$$T_{21} = T_{12} (2.26)$$

De la misma forma al insertar el Reflect, se obtiene el diagrama de bloques y el grafo de flujo de señales de la figura 2.19 (b). Del grafo se obtiene la ecuación 2.27, de simetría se obtiene la ecuación 2.28, y notando que los puertos quedan desacoplados se obtiene la ecuación 2.29.

$$R_{11} = S_{11} + \frac{S_{12}^2 \Gamma_L}{1 - S_{22} \Gamma_L} \tag{2.27}$$

$$R_{22} = R_{11} (2.28)$$

$$R_{12} = R_{21} = 0 (2.29)$$

Finalmente al insertar Line se obtienen el diagrama de bloques y el grafo de flujo de señales de la figura 2.19 (c). Al igual que en el caso del T Del grafo se obtienen las ecuaciones 2.30 y 2.31, mientras que de reciprocidad y simetría se obtienen 2.32 y 2.33.

$$L_{11} = S_{11} + \frac{S_{22}S_{12}^2 e^{-2\gamma\ell}}{1 - S_{12}^2 e^{-2\gamma\ell}}$$

(2.30)

$$L_{12} = \frac{S_{12}^2 e^{-\gamma \ell}}{1 - S_{22}^2 e^{-2\gamma \ell}} \tag{2.31}$$

$$L_{22} = R_{11} (2.32)$$

$$L_{21} = R_{12} (2.33)$$

Con esto se obtienen 5 ecuaciones: 2.23, 2.24, 2.27, 2.30 y 2.31; y 5 incógnitas  $S_{11}$ ,  $S_{22}$ ,  $S_{12}$ ,  $\Gamma_L$  y  $e^{-\gamma \ell}$  que corresponde al factor de propagación. De aquí se pueden calcular los parámetros S de los bloques de error, con lo que concluye la calibración. Finalmente con los bloques de error caracterizados, al medir el dispositivo en la configuración de la figura 2.18 se estará midiendo la matriz  $ABCD^m$  dada por 2.34. Luego los parámetros S del DAM dados por su matriz equivalente ABCD' se obtiene en la ecuación 2.35 donde se realiza el deembed de los bloques de error de la medición de todo el sistema.

$$ABCD^{m} = \begin{bmatrix} A^{m} & B^{m} \\ C^{m} & D^{m} \end{bmatrix}$$

(2.34)

$$\begin{bmatrix} A' & B' \\ C' & D' \end{bmatrix} = \begin{bmatrix} A & B \\ C & D \end{bmatrix}^{-1} \begin{bmatrix} A^m & B^m \\ C^m & D^m \end{bmatrix} \begin{bmatrix} A & B \\ C & D \end{bmatrix}$$

(2.35)

Se puede ver del método descrito, que no es necesario conocer  $\Gamma_L$  del standard Reflect, ni el largo, ni las perdidas de Line, ya que se determinan durante la calibración, al resolver el sistema de ecuaciones. Esto es la característica que hace confiable esta calibración cuando no se dispone de la precisión para crear los standards.

como cómo de pregunta

**Figura 2.19:** Diagrama de Bloques y grafos de flujos de señales de standards de calibración TRL. (a) Throu. (b) Reflect. (c) Line.

# Capítulo 3

# Desarrollo

# 3.1. Descripción del Sistema de medición

A continuación se da una descripción general del sistema de medición con el cual se obtienen los parámetros S del transistor, que posteriormente serán procesados para obtener la su caracterización. El diseño y construcción de los componentes de este sistema sera cubierto en detalle más adelante.

Las mediciones se efectúan con un VNA (Vector Network Analyzer) modelo E8364C de Agilent. Este equipo se utiliza para obtener los parámetros S de una red. Para esto envía señales alternas a los puertos del circuito y mide voltaje y fase de las señales que se reflejan o transmiten por el circuito y se devuelven al VNA. El VNA utilizado es de dos puertos, para medir redes de más puertos es necesario realizar más de un montaje de medición con el VNA.

En la figura 3.1 se ve el diagrama de bloques del sistema de medición. El puertos 1 del VNA se conectan por cable coaxial al puerto 1 del bloque Bias Tee 1, a este último ingresa además el voltaje continuo de la fuente de polarización por el puerto 3, ambos voltajes se mezclan al interior de este bloque para salir por el puerto 2 por medio de cable coaxial, que llega al puerto 1 del bloque del transistor. De manera simétrica se conecta el puerto 2 del VNA al puerto 2 del bloque del transistor. La única asimetría esta en que el puerto 1 del bloque del transistor se conecta al pad Gate del transistor, mientras que el puerto 2 de este

Figura 3.1: Diagrama de conexión del sistema de medición.

bloque se conecta al *pad Drain* del dispositivo. El resto de las conexiones son simétricas, lo que es importante en la calibración TRL como se vera más adelante. Por esto, es importante que ambos bloques Bias Tee sean construidos lo más semejantemente posible.

Las señales viajan en los bloques del transistor y los de Bias Tee por medio de líneas microstrip. La adaptación de línea coaxial a microstrip y de microstrip a coaxial que se realiza en los puertos 1 y 2 de los tres bloques mencionados, se hace por medio de conectores 2.4 mm modelo PE44221 (macho) [6] y PE44218 (hembra) [7] de Pasternack Enterprises. La señal continua ingresa al puerto 3 de los bloques Bias Tee por medio de un conector SMA PE4001 (hembra) [8] de Pasternack Enterprises, que hace la transformación a microstrip. En la figura 3.2 se pueden ver los conectores mencionados.

Dado que los transistores a medir, los cables coaxiales y el VNA tienen una impedancia de  $50 \Omega$ , para evitar perdidas y reflexiones debidas a desadaptación de impedancia, se diseñan

todos los componentes del sistema de calibración en 50  $\Omega$ . Esto incluye el Bias Tee y los standards de la calibración TRL.

Figura 3.2: Conectores. (a) 2.4 mm macho. (b) 2.4 mm hembra. (c) SMA hembra.

# 3.2. Transistor a Utilizar

El sistema de caracterización esta diseñado para trabajar con una variedad de transistores HEMT, sin embargo, cada transistor debe ir montado en un bloque acorde a las dimensiones físicas del dispositivo. El sistema descrito en esta memoria fue diseñado para caracterizar el transistor pHEMT modelo EC2612 [9] marca UMS [10].

En la figura 3.3 se puede ver el esquema del transistor en cuestión y sus dimensiones físicas en  $\mu m$ . Se puede ver que Gate y Drain tienen un pad de conexión cada uno y que existen dos pads para source. Estos últimos están conectados a la metalización posterior del transistor, lo que permite conectarlos directamente a tierra.

# 3.3. Bias Tee

El Bias Tee se encarga de tomar la señal proveniente del VNA y mezclarla con el voltaje continuo proveniente de la fuente de polarización, de modo de poder entregar señal y polarización al transistor HEMT por el mismo canal, tal como operan estos dispositivos.

Figura 3.3: Esquema de transistor pHemt EC2612 con dimensiones físicas en  $\mu m$ .

Al mezclar la señal con la polarización, se debe cuidar que la señal no ingrese por el canal de polarización hacia la fuente, ni que el voltaje continuo ingrese por el canal de la señal hacia el VNA, ya que en ambos casos se pueden dañar estos dispositivos. Por esta razón, la mezcla de voltajes se debe hacer en este bloque y no directamente en el bloque del transistor. Se usará como convención que el puerto por el que ingresa la señal proveniente del VNA sera llamado puerto 1, el puerto 3 será por donde ingresa el voltaje de polarización y por el puerto 2 saldrán la señal y la polarización mezcladas. Además, el Bias Tee debe permitir que señales que ingresen por el puerto 2 puedan llegar al puerto 1, sin introducirse en el puerto 3.

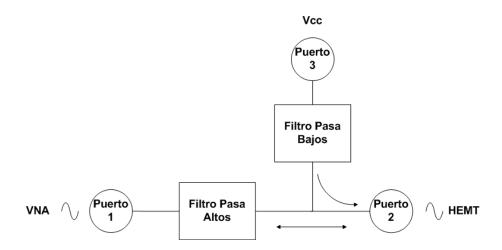

La estructura básica del Bias Tee se compone de dos filtros, como se ve en la figura 3.4. Un filtro pasa altos se encarga de evitar que el voltaje continuo salga por el puerto 1. Un filtro pasa bajos se encarga de evitar que las señales de los puertos 1 y 2 salga por el puerto 3.

Es importante que en el filtro pasa altos el conductor esté cortado para garantizar el filtrado del voltaje continuo. En este caso, la señal de alta frecuencia debe pasar por el filtro

Figura 3.4: Diagrama de bloques del filtro Bias Tee.

| Altura de substrato                | $10 \ mil^{-1}$ |

|------------------------------------|-----------------|

| Altura cada capa de cobre          | $35 \ \mu m$    |

| Constante dieléctrica $\epsilon_r$ | 2.94            |

| Factor de disipación TAN $\delta$  | 0.0012          |

Cuadro 3.1: Parámetros substrato RT/duroid 6002.

por medio de un campo magnético o un campo eléctrico. De esta forma este filtro puede estar basado tanto en líneas acopladas como en la utilización de condensadores.

### 3.3.1. Diseño del Bias Tee

El Bias Tee estará fabricado en microstrip RT/duroid®6002 en cobre [11] de Rogers Corporation [12]. Las características del substrato se presentan en el cuadro 3.1.

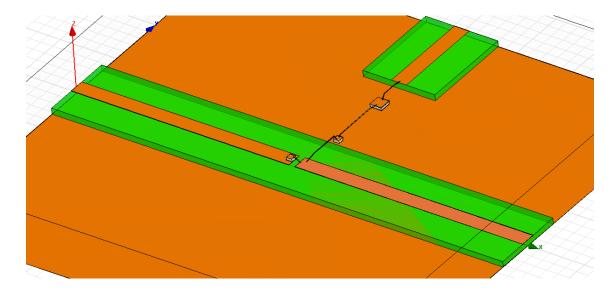

Se realizaron simulaciones en Ansoft Designer para obtener un diseño funcional y luego se construyó un modelo en Ansoft HFSS para obtener una simulación más precisa del comportamiento del circuito. El diseño final obtenido en HFSS del Bias Tee se puede ver en la figura 3.5, donde el color naranjo representa al cobre, el verde al substrato duroid 6002, el

$<sup>^1</sup>mil$ : unidad de medida de longitud del sistema imperial. Esta definida como milésima de pulgada. 1 mil equivale a 25.4  $\mu m$ .

Figura 3.5: Renderización del modelo en HFSS del Bias Tee.

blanco al substrato de los condensadores y el amarillo a los bondings de oro. Estos últimos pueden ser vistos como líneas negras dependiendo de la escala de la renderización del modelo. A la izquierda está el puerto 1, que es el que irá conectado al VNA; a la derecha el puerto 2, encargado de llevar el bias y la señal alterna hacia el transistor; y arriba se encuentra el puerto 3, que va conectado a la fuente de voltaje continuo.

El ancho de las líneas microstrip es Calculado en Ansoft Designer para obtener impedancia de 50  $\Omega$ . Para esto se ingresa al programa las caracteristicas del substrato RT/duroid 6002 y la frecuencia a la que se quiere calcular la impedancia. Las líneas fueron calculadas para una frecuencia intermedia de 38 GHz.

Los filtros están diseñados en base a condensadores e inductancias lumped. Se dispone en el laboratorio de un pack de condensadores de microonda, por lo que se cuenta con valores discretos de capacitancia al diseñar el circuito. Los valores relevantes para el rango de frecuencia son 0.1pF, 0.4pF, 0.6pF, 1pF y 100 pF. Las inductancias se construyen con bondings de oro. Ya que HFSS sólo trabaja con los parámetros físicos del bonding, el valor de inductancia modelado sólo se puede calcular fuera del programa usando la aproximación de

| Cap $[pF]$ | Dimensiones $[mil]$ | Altura [mm] | k       |

|------------|---------------------|-------------|---------|

| 0.1        | 10×10               | 0.1         | 22.23   |

| 0.4        | 10×10               | 0.1         | 88.93   |

| 0.6        | 10×10               | 0.1         | 133.4   |

| 1          | 10×10               | 0.1         | 222.32  |

| 100        | 20×20               | 0.1         | 4376.56 |

Cuadro 3.2: Parámetros substrato RT/duroid 6002.

que el valor de inductancia será de 1 nH por cada mm de largo que tenga el bonding.

Los condensadores en HFSS son modelados construyendo dos placas paralelas separadas por un dieléctrico. Las dimensiones del modelo corresponden a las nominales de cada condensador real. El valor de capacitancia de cada condensador queda especificada por la constante de permitividad relativa k de su dieléctrico. Dado que esta constante no se encuentra en el datasheet, debe ser calculada según la formula 3.1. El cuadro 3.2 muestra los parámetros de los condensadores utilizados y la constante k calculada.

$$Capacitancia = \frac{k \times \epsilon_0 \times A}{d} [F] \tag{3.1}$$

Donde A es el área de las placas paralelas del condensador, d es la distancia que separa las placas, ambas medidas en unidades del Sistema Internacional y  $\epsilon_0 = 8,854 \times 10^{-12} \ F/m$ .

**Figura 3.6:** Renderización de los Filtros del Bias Tee en mayor detalle. (a) Filtro pasa altos. (b) Filtro pasa bajos.

Figura 3.7: Diagrama circuital del Bias Tee.

El diagrama circuital en donde se presentan los elementos del Bias Tee se puede ver en la figura 3.7. En el diseño obtenido del filtro pasa altos la línea microstrip que sale del puerto 1 se conecta en serie a  $C_1$  que esta montado sobre ella, como se ve en la figura 3.6 (a). El condensador se une a la línea microstrip que va al puerto 2 por medio del bonding de oro  $B_1$ . el voltaje continuo del puerto 3 queda aislado del puerto 1 por el dieléctrico del condensador  $C_1$ . Más aún el filtro L-C formado por  $C_1$  y  $B_1$  en serie, se encarga de filtrar señales alternas de baja frecuencia.

En el filtro pasa bajos los bondings  $B_2$ ,  $B_3$  y  $B_4$  se conectan en serie para unir el circuito principal con el puerto 3. Las uniones de estos bondings estan nontadas sobre los condensadores  $C_2$  y  $C_3$  que están en paralelo. Este filtro de bondings largos y condensadores en paralelo, tal como se ve en las figuras 3.7 y 3.6 (b), tiene una impedancia bastante mayor que el circuito principal. La señal que viaja del puerto 1 al 2, o viceversa, se encuentra con una alta impedancia en la rama que va hacia el puerto 3, por lo que no ingresa por esta rama.  $C_3$

| Curva    | $C_1[pF]$ | $C_1 k$ | Color  |

|----------|-----------|---------|--------|

| $S_{11}$ | 0.1       | 22.23   | Rojo   |

| $S_{11}$ | 0.4       | 88.93   | Azul   |

| $S_{11}$ | 1         | 222.32  | Rosado |

| $S_{12}$ | 0.1       | 22.23   | Verde  |

Cuadro 3.3: Código de colores de parámetros S para las figuras 3.8, 3.9 y 3.10.

de mayor capacitancia se encarga de filtrar señales de baja frecuencia que puedan ingresar por la rama del puerto 3.

En el Bias Tee, el espacio que interrumpe transversalmente la línea que va del puerto 1 al puerto 2 es un factor determinante. El parámetro gap da cuenta de esta distancia en el modelo. El gap representa el parámetro más crítico del circuito, ya que define el largo del bonding  $B_1$ , que es determinante en el filtro L-C del circuito pasa altos. Además, por sus pequeñas dimensiones, al rededor de los 10 mil, es la especificación más difícil de construir y la limitante física del diseño. Por esta razón se modeló  $B_1$  parametrizado por el largo del gap. Luego mientras más pequeño el gap menor inductancia tendrá  $B_1$ .

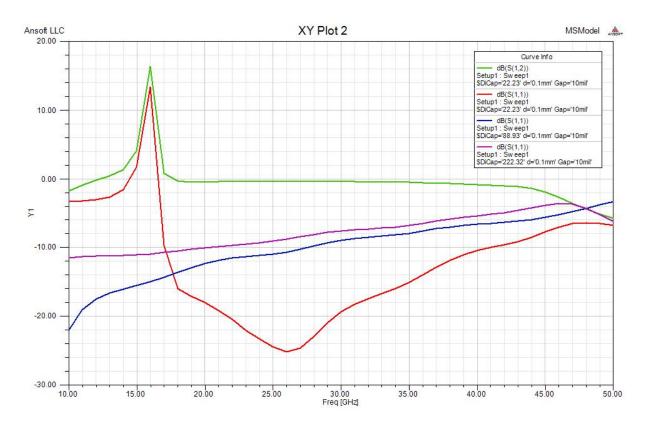

Los resultados obtenidos del modelo en HFSS para el filtro pasa altos se pueden ver a continuación. La figura 3.8 muestra los parámetros S del circuito para un gap de 6 mil, donde aparecen la transmisión  $S_{12}$  para un condensador de 0.1 pF (la que dio mejores resultados), y la reflexión  $S_{11}$  para valores de condensador de 0.1, 0.4 y 1 pF. En el modelo los condensadores están parametrizados por su constante de permitividad relativa k, la que está representada por el parámetro DiCap. Los gráficos de las figuras 3.9 y 3.10, muestran las mismas curvas, pero para valores de gap de 6 y 10 mil respectivamente. La nomenclatura para los gráficos en las figuras 3.8, 3.9 y 3.10, se muestra en el cuadro 3.3.

Se puede ver de los gráficos en las figuras 3.8, 3.9 y 3.10, que el valor de capacitancia más apropiado para  $C_1$  independiente del largo de  $B_1$  es 0.1 pF. Observando las curvas  $S_{11}$  para 0.1 pF, se tiene que para 10 mil en la figura 3.10 el filtro se centra en torno a los

**Figura 3.8:** Simulación de Bias Tee en HFSS, con gap de 6 mil, para valore de  $C_1$  de 0.1, 0.4 y 1 pF.

27GHz con el rango de 19-35 GHz bajo los -15dB. Para 8 mil en la figura 3.9 se centra en los 29 GHz con el rango de 19-38 GHz bajo los -15 dB. Para 6 mil en la figura 3.8 se centra en los 33 GHz con el rango de 22-44 GHz bajo los -15dB. Para los otros valores de capacitancia se obtienen reflexiones mayores, donde  $S_{11}$  no baja de los -15 dB entre los 25 y 50 GHz para ninguno de los tres gráficos. Dado que el transistor deberá funcionar para el rango de 30-50 GHz, el ideal es construir un Bias Tee que funcione en este rango para poder caracterizar el transistor en su frecuencia de operación. Como se ve en los gráficos, para centrar el filtro pasa altos a mayor frecuencia se tendría que disminuir el gap bajo los 6 mil.

Los parámetros críticos del modelo en HFSS son el  $B_1$ ,  $C_1$ ,  $B_2$  y  $C_2$ . Siendo el primero el más crítico, dado que no se dispone de un condensador de menor capacitancia que 0.1 pF, se debe acortar  $B_1$  para lograr centrar el filtro pasa altos en la frecuencia deseada. Por motivos

**Figura 3.9:** Simulación de Bias Tee en HFSS, con gap de 8 mil, para valore de  $C_1$  de 0.1, 0.4 y 1 pF.

constructivos el gap no puede ser menor a 6 mil, siendo este último un valor ya bastante difícil de obtener, lo que acota el largo mínimo de  $B_1$  a 0.76 mil.

## 3.3.2. Construcción de Componentes

### Bloque de Montaje

El bloque metálico donde va montado el circuito del Bias Tee fue mecanizado en una fresadora de control manual en el taller mecánico del DAS. El material de construcción es duraluminio, que posee buena conductividad y resistencias mecánica.

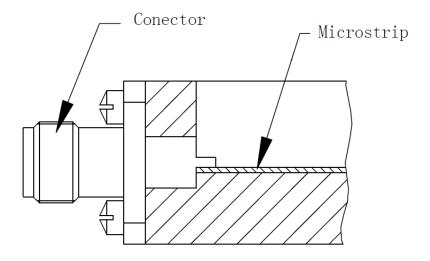

El bloque forma una caja con un orificio de fondo cuadrado de 20 mm de lado. La profundidad del orificio, el grosor de la pared y la altura de la caja están diseñados ajustar a las

**Figura 3.10:** Simulación de Bias Tee en HFSS, con gap de 10 mil, para valore de  $C_1$  de 0.1, 0.4 y 1 pF.

dimensiones de los conectores 2.4 mm y SMA. El grosor de la pared debe ser igual al largo del dieléctrico que cubre el pin de los conectores. La altura de la caja debe ser suficiente para poder montar los conectores en la pared. La profundidad del orificio debe ser tal que el pin de los conectores quede posado sobre la línea microstrip, para esto se debe considerar además de la altura de la línea microstrip, la altura extra que agrega el pegamento con que la línea va sujeta al bloque, que corresponde a cianoacrilato. La elección del pegamento será discutido más adelante. En la figura 3.11 se puede ver un diagrama que muestra el montaje de un conector 2.4 mm en la pared de la caja.

Figura 3.11: Diagrama de montaje de conector en pared del bloque de duraluminio.

#### Líneas Microstrip

La fabricación de las líneas microstrip constituye uno de los factores limitantes en la obtención del filtro diseñado. Las dimensiones arrojadas por por las simulaciones son difíciles de obtener sin una maquinaria especializada. El substrato escogido (TR/duroid 6002) se compone de dos placas de cobre muy delgadas que rodean una capa de dieléctrico, esto conforma una plancha. Para crear un circuito en esta plancha es necesario remover todo el cobre de la placa superior que no forme parte del circuito, de manera que quedara en la cara superior un circuito metálico dibujado sobre el substrato y en la cara inferior se tendrá una placa de cobre completa, la que corresponde al plano de tierra. Se puede extraer también todo el metal de la cara inferior si se sabe que el substrato ira pegado directamente sobre un conductor conectado a tierra.

Se estudiaron tres métodos de construcción para extraer el cobre sobre el dieléctrico:

#### ■ Fresado en CNC

#### • Fresado en LPKF

#### Método fotoresistivo

Los primeros dos métodos consisten en pegar el substrato con cianoacrilato a una placa más rígida que va montada en la fresadora. La CNC es una fresadora con control numérico por computador de la que dispone el DAS. Tiene gran precisión y su satisfactorio desempeño fue comprobado en trabajos similares [13], pero su alto nivel de demanda y la existencia de otros métodos de construcción descartaron su utilización. La LPKF es una fresadora para crear circuitos impresos disponible en el DIE. Se realizaron pruebas de fabricación de circuitos microstrip que no dieron los resultados esperados. Si bien los cortes de la LPKF en el plano del circuito fueron lo suficientemente precisos para generar el circuito deseado, esta máquina esta diseñada para cortar substratos más gruesos, por lo que se presentaron dos problemas. En primer lugar la máquina se apoya sobre el circuito para realizar el fresado, por lo que al trabajar con RT/duroid 6002, raspa la delgada placa de cobre desgarrando los contornos ya generados. En segundo lugar los cortes producidos por la fresa son muy disparejos, por lo que era necesario realizar varias pasadas de fresado para lograr sacar una capa de cobre, donde cada vez se bajaba un delta la altura de la fresa. Esto resultó con sectores en el substrato con cortes muy poco profundos donde se logro sacar exitosamente el cobre, pero con otros donde la fresa había atravesado el substrato. Tener alturas de substrato distintas a la nominal cerca de las líneas implica que el campo eléctrico tendrá menos dieléctrico entre la línea y la tierra, lo que alterará el comportamiento esperado del circuito.

El circuito fue construido usando el método fotoresistivo. Éste consiste en imprimir el circuito requerido en una lamina transparente, luego aplicar la pintura fotosensible Positiv20 sobre la lamina de cobre del substrato donde irá impreso el circuito. Al aplicar luz ultravioleta sobre la cara pintada de cobre con la lamina transparente sobrepuesta, se debilitara la pintura expuesta a la luz (las áreas donde la transparencia no tenia impreso parte del circuito), luego se sumerge el substrato en soda caustica hasta que solo quede la pintura dibujando el circuito deseado. El substrato se sumerge finalmente en cloruro férrico donde

el cobre que no este protegido por la pintura será extraído del dieléctrico quedando solo el circuito impreso en la capa superior de cobre. En este último paso si no se quiere perder la capa de cobre inferior que hace de tierra, es necesario cubrirla con alguna protección contra el cloruro férrico, esmalte de uñas puede servir para esta tarea. Finalmente se limpia la pintura fotoresistiva y el esmalte si fue aplicado de las placas de cobre con acetona, obteniéndose el circuito deseado. Los pasos para realizar este método están detallados en el anexo A.1 de [13].

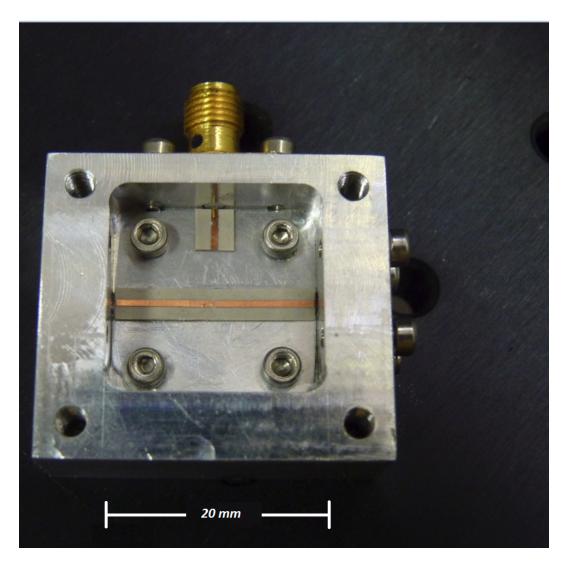

Figura 3.12: Fotografía de las líneas microstrip fabricadas.

Durante la fabricación, varias líneas fueron producidas en el mismo proceso sobre la misma placa de dieléctrico, luego el substrato fue guillotinado para separar las lineas en rectángulos independientes. La regla para los cortes es que a cada lado de la línea debe haber un área de substrato de ancho al menos 2.5 veces el ancho de la linea. Ésto asegura que el campo eléctrico se cierre a tierra a través del dieléctrico y no del aire en el borde de la rectángulo.

Las líneas obtenidas se muestran en la figura 3.12.

Se puede observar que este método no es del todo satisfactorio. De las líneas producidas se escogen las más adecuadas desechando al menos el doble de líneas defectuosas o menos aptas. Aun así las líneas escogidas muestran una deficiencia en el gap y sus bordes son disparejos. Siendo el primero el problema más relevante. Por esta razón, en la etapa de diseño no se fijo una distancia para el gap, si no que se estudio su comportamiento para un rango de valores de 6 a  $10 \ mil$ , donde se espera que este método pueda producir un gap entre estos valores.

## 3.3.3. Montaje del Bias Tee

Al perforar en el bloque metálico los forados para los conectores 2.4 mm la broca deja una cavidad en el suelo de la caja. Se detecto durante el montaje que las líneas se doblaban hacia abajo por la presión al contacto con los conectores en esta zona donde existe esta cavidad. Por esta razón, se decidió instalar en primer lugar una lamina de aluminio sobre el fondo de la caja, de forma de tapar estos resquicios. Esta lamina va afirmada por cuatro tornillos al bloque de duraluminio, esto además de sujetarla, asegura su conexión a tierra, ya que no se tiene certeza que la lamina quede bien apoyada al fondo de la caja. De ahora en adelante la referencia al fondo de la caja incluirá a la lamina montada sobre éste.

#### Elección Del Pegamento

En la elección del pegamento a utilizar se consideraron las siguientes opciones:

- Pintura de plata

- Cianoacrilato

- Pegamento Epóxico

La pintura de plata es un pegamento conductor de fraguado lento, lo que lo convierte en un buen candidato. Sin embargo durante pruebas de montaje de prototipos se observó que si bien esta pintura es de fácil de extraer con acetona, minúsculos residuos quedan adosados al substrato. Éstos al ser conductores pueden actuar como puntos de acumulación de carga que pueden interferir en el funcionamiento del circuito. Por esta razón fue descartada su utilización.

El cianocrilato es de fraguado rápido lo que dificulta su utilización, pero tiene la ventaja de su fácil extracción con acetona y que no deja residuos. Al no ser un material conductor se descarta su utilización en aplicaciones donde se requiera esta característica.

El pegamento epóxico es conductor y de fraguado lento. Es fácil de limpiar mientras no se haya cosido, lo que permite corregir errores de montaje. Una vez cosido resulta muy difícil de sacar. La experiencia mostró que después de 48 horas sumergido en cloroformo no se logro despegar un condensador de un bloque de duraluminio pegado con este método.

Se utilizará entonces cianoacrilato para pegar las líneas al fondo de la caja donde no se necesita un material conductor. Se estima que el efecto de agregar un segundo dielectrico (cianoacrilato) de mucho menor espesor entre el substrato y el bloque, no cambiara el desempeño del circuito. Los condensadores serán pegados con pegamento epóxico debido a la dificultad de su montaje, por lo que se necesita tiempo para montarlos correctamente. Además este pegamento asegurara el contacto eléctrico de la placa inferior del condensador con la superficie donde será pegado.

#### Líneas Microstrip

Las líneas que van del puerto 1 al 2 se pegaron con cianoacrilato al fondo de la caja intentando dejarlas alineadas entre los agujeros por donde ingresan los conectores 2.4 mm.

La línea que va al puerto 3 se pega de la misma manera, como solo se espera que pase un voltaje continuo por ella, la alineación con el pin del conector SMA no es importante, solo basta que el conector tenga una superficie de contacto adecuada sobre el cobre la línea.

El montaje de las líneas se puede ver en la figura 3.13.

Figura 3.13: Fotografía de las líneas microstrip montadas sobre el bloque de duraluminio.

Dado que el bloque metálico fue fresado en una fresadora con control manual, resulta inevitable tener pequeñas imprecisiones. Éstas afectan por sobre todo la alineación de las

entradas de los conectores 2.4 mm por lo que resulta difícil alinear la línea principal con los pines de los conectores centrados en ella en ambos lados.

#### Condensadores

Los condensadores fueron pegados con pegamento epóxico.  $C_1$ , es el más critico, debe ir lo más cercano al borde de la línea que sea posible de forma que el bonding  $B_1$  tenga la mínima longitud al sobrepasar el gap. Se debe cuidar que su base quede totalmente sobre la línea para que al realizar el bonding no se rompa o desprenda la línea o el condensador.  $C_2$  y  $C_3$  van pegados sobre el fondo de la caja.

En la figura 3.14 se puede ver el montaje de líneas y condensadores.

#### Bondings de Oro

Con el resto de los elementos ya montados sobre el bloque metálico se procede a realizar los bondings. Para esto se utiliza la Bonding Machine modelo 4526 de la empresa Kuliche & Soffa [14] disponible en el laboratorio de Instrumentación Astronómica del DIE. Esta máquina permite realizar conexiones eléctricas entre objetos de pequeñas dimensiones por medio de un hilo de oro llamado bonding, por lo que esta máquina está dotada de gran precisión, un control automatizado y un microscopio para operarla. El detalle de su operación puede ser visto en [13].

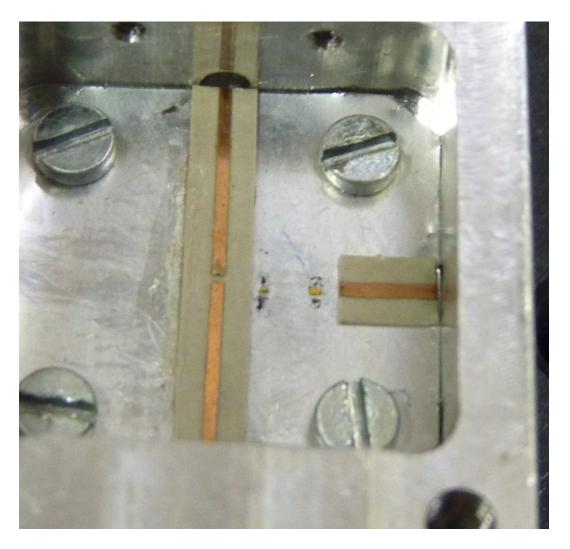

# 3.4. Bloque del Transistor

Los componentes del bloque del transistor son similares a los de las Bias Tee pero sin la rama de polarización. Un par de conectores 2.4 mm en caras opuestas conectan a líneas microstrip que viajan hacia el dispositivo, un bonding se encarga de unir la línea proveniente

Figura 3.14: Fotografía de condensadores y líneas montados sobre el bloque de duraluminio.

del puerto 1 con el *pad Gate* del transistor, y otro se encarga de unir la línea proveniente del puerto 2 con el *pad Drain*. Los *pads Source* estan conectados a la cara inferior del transistor, que debe ir conectada a tierra.

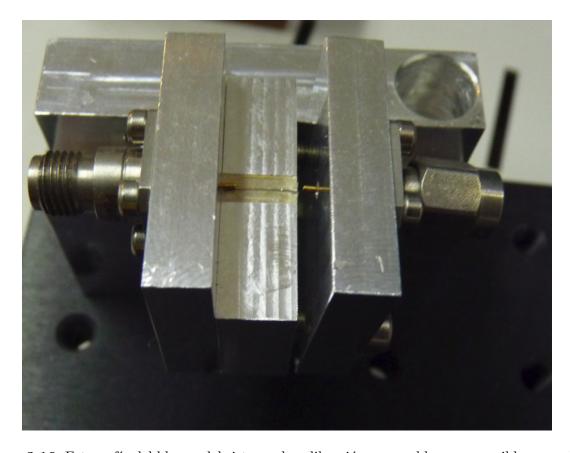

Dado que se creo un bloque de conexiones rápidas para la calibración TRL, como se vera en la siguiente sección, se aprovechara este sistema para crear el bloque de montaje del transistor de manera compatible con este sistema.

Para el bloque del transistor y los bloques de los standards TRL el substrato microstrip

| Altura de substrato                | 5 mil     |

|------------------------------------|-----------|

| Altura cada capa de cobre          | $9 \mu m$ |

| Constante dieléctrica $\epsilon_r$ | 2.05      |

| Factor de disipación TAN $\delta$  | 0.00045   |

Cuadro 3.4: Parámetros substrato CuFlon.

utilizado es CuFlon de Polyflon Company [15], cuyas características se pueden ver en el cuadro 3.4.

El cambio de substrato se debe a que CuFlon presenta menores perdidas que RT/duroid 6002 y dado que por la precisión de los *standards* éstos requieren ser fabricados en la CNC, el menor grosor del substrato no representara un problema, como lo sería su fabricación por método fotoresistivo.

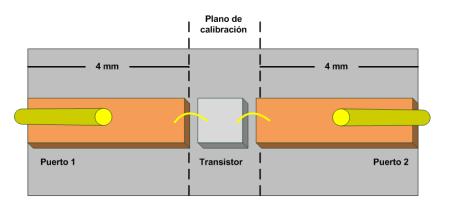

Las líneas que llevan la señal desde los puertos al transistor son de  $50~\Omega$  y de un largo de 4~mm, este largo se consideró de manera que la onda se pueda adaptar de coaxial a microstrip antes de llegar al bonding del transistor. Éstas van pegadas con cianoacrilato al bloque metálico.

Entre las líneas se deja un espacio de 0.5 mm donde va montado el transistor que tiene 0.38 mm de ancho, lo que deja una distancia muy pequeña para que los bondings que unen el dispositivo a las líneas no tengan un elevado valor de inductancia. La cara inferior del transistor da la conexión a tierra, por lo que debe ser pegado con pegamento conductor. Como ya se menciono se utilizara pegamento epóxico, el que debe ser cuidadosamente aplicado para no formar cortocircuitos en el transistor, en las líneas o entre ambos.

# 3.5. Calibración TRL

## 3.5.1. Elección del Plano de Calibración

El diseño del sistema de calibración TRL es dependiente del lugar donde se sitúe el plano de calibración.

El objetivo de la calibración es descontar de la medición del dispositivo todos los efectos de los elementos conectados entre éste y el VNA. Los elementos descontados serán todos los que estén situados detrás de plano de calibración. Por este motivo el ideal es colocar el plano de calibración lo más cercano posible al dispositivo.

Figura 3.15: Diagrama que muestra el plano de calibración TRL en el bloque del transistor.

Los bondigs que unen el transistor a las líneas no pueden ser incluidos dentro de la calibración, por lo que se tendrá que hacer un *deembed* de estos posteriormente. De esta forma lo más cercano que se puede llevar el plano de calibración al transistor es hasta antes de estos bondings. De esta forma la calibración TRL estará descontando todos los cables coaxiales del sistema de medición, los Bias Tee y dentro del bloque del transistor, los conectores 2.4 mm y las líneas microstrip que llevan la señal al transistor.